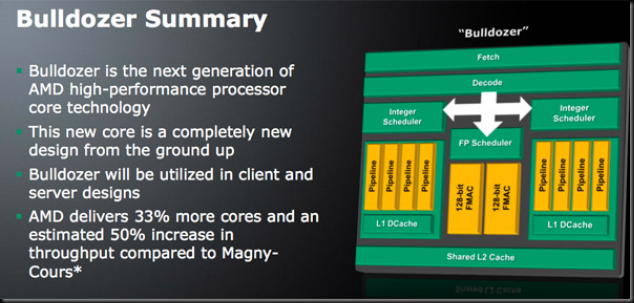

Parece que AMD ha desvelado por fin algunos detalles arquitecturales de su nuevo diseño destinado a servidores y sobremesas de gama alta: AMD Bulldozer.

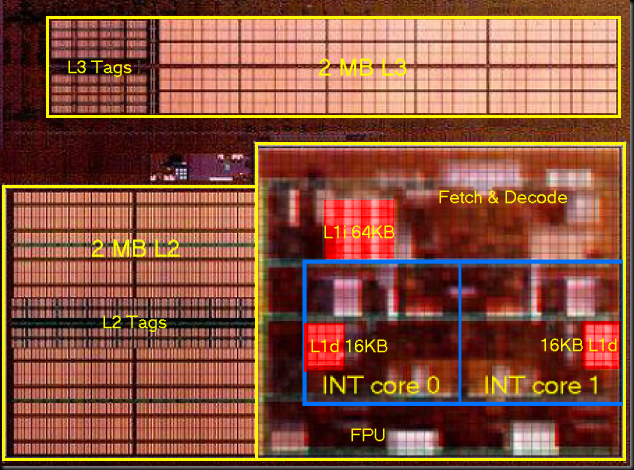

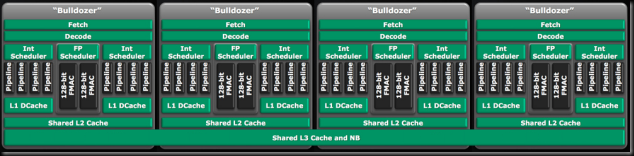

Uno de los módulos de AMD Orochi, el primer integrante de la familia Bulldozer.

Uno de los módulos de AMD Orochi, el primer integrante de la familia Bulldozer.

He publicado un artículo ampliado sobre el concepto de diseño de Bulldozer en LowLevelHardware:

- Intel Core i7 SMT vs. AMD Bulldozer CMT – LowLevelHardware 25 Agosto 2010

Y un segundo escrito profundizando más en su novedosa microarquitectura:

- La microarquitectura de AMD Bulldozer – LowLevelHardware 11 Septiembre 2010

Hasta ahora nos movíamos más en el terreno de la especulación que en el de los hechos, finalmente podemos hablar con fundamento real de este avanzado procesador que estará a la venta a mediados de 2011.

En varios artículos pasados de algunos de mis Blogs he analizado esta microarquitectura, en algunos de ellos en bastante detalle incluso estimando sus prestaciones:

- Previo AMD Bulldozer. Actualizado – LowLevelHardware 06 Diciembre 2009

La próxima generación del core de AMD está despertando una gran excitación entre los profesionales de la arquitectura de procesadores, e incluso entre los propios ingenieros en Intel. Tal como ahora la conocemos será un rotundo éxito si es llevada a buen puerto como apuntan los numerosos rumores y las escuetas informaciones del fabricante.

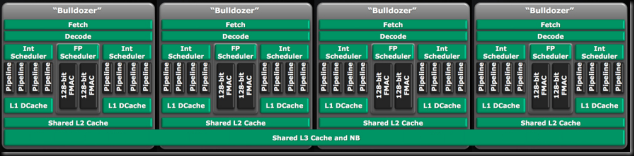

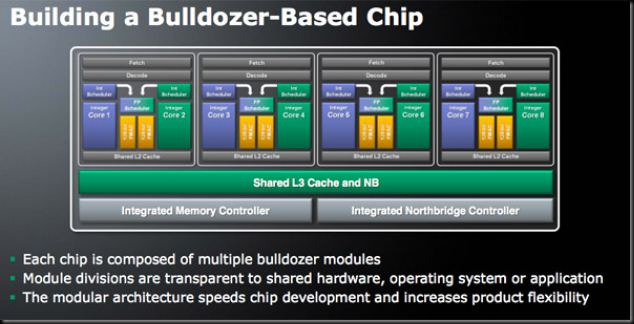

AMD Bulldozer Zambezi 8 cores: 4 módulos y 8 threads con 8 INT cores.

La composición de módulos Bulldozer de arriba creó controversia en su día pues se afirmaba que las cachés L2 eran también compartidas por todos los cores, algo para mí absurdo. La única caché globalmente compartida es la L3 o LLC (Last Level Cache).

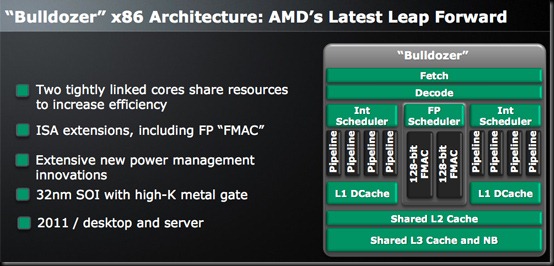

AMD ha diseñado y tiene ya finalizado el floorplan del nuevo procesador que en 2011 inaugurará una nueva microarquitectura. Un concepto revolucionario en muchos aspectos que no por ello deja de suscitarme algunas dudas acerca de su rendimiento single thread.

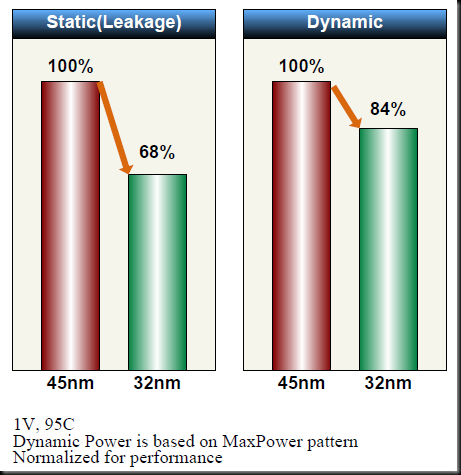

Será fabricado para AMD por Global Foundries en el proceso de 32 nm SOI high-k metal gate ya que AMD se deshizo de sus fábricas de semiconductores (wafers).

Los orígenes de Bulldozer:

- AMD Bulldozer. Prestaciones estimadas – LowLevelHardware 25 Febrero 2010

En el tercero de esta serie de artículos dedicados a la próxima microarquitectura de AMD voy a aventurar mis previsiones sobre su nivel prestacional. Además lo compararé con los diseños actuales y con su muy evolucionado y perfeccionado futuro competidor, Intel Sandy Bridge.

Cada día salen a la luz algunas nuevas informaciones sobre los nuevos procesadores destinados a servidores y la gama alta de sobremesa y estaciones de trabajo, los nuevos Bulldozer.

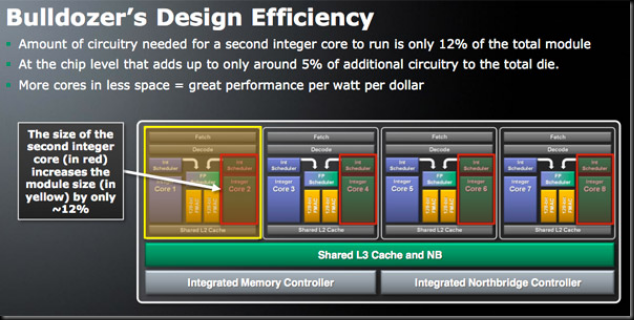

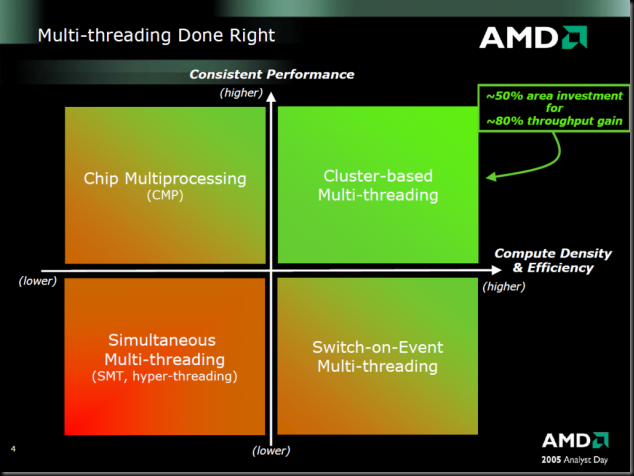

Como sabréis, Bulldozer supone un cambio importante para AMD y en general para el mundo X86, una verdadera revolución en el diseño dado que se comparten entre cores algunas estructuras de procesamiento, en este caso la unidad FPU y el FP scheduler.

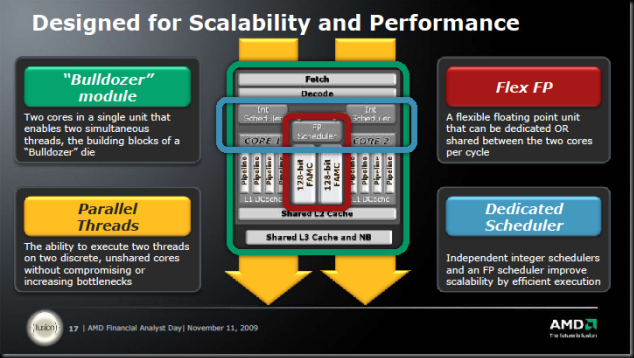

Un módulo Bulldozer consta de dos cores de enteros.

Debido a estos artículos y por la opiniones que en ellos he expresado (todas basadas en hechos físicos experimentales y conocimientos sobre microarquitectura) me he metido en algunas “discusiones” microarquitecturales con algunos integrantes de ciertos foros que suponían que Bulldozer iba a ser una arquitectura absolutamente superior a todo lo conocido.

Extraído de Microarquitectura AMD Bulldozer 2011. Actualizado – LowLevelHardware 21 Febrero 2010

Hipótesis 1: Si AMD utiliza 4 pipelines para cálculo entero y simultáneamente como AGUs (Address Generation Units) o 2 pipelines de enteros y dos AGUs, la potencia de proceso descendería drásticamente en algunos algoritmos… incluso respecto al actual Shanghai 45 nm (Phenom II) core for core y clock for clock.

He leído a algunos ingenieros de AMD e incluso a alguien de su Staff directivo alabar las cualidades de proceso multi thread de Bulldozer y eludir comentarios sobre potencia de cálculo single thread. Sinceramente, espero haber entendido mal sus comentarios…

En este caso, a igualdad de reloj y en procesos single threaded sería más rápido un Phenom II actual que este hipotético Bulldozer aunque tuviese muchos más cores disponibles para ejecutar más threads.

Por supuesto, en este caso Intel no tendría competencia en software single threaded. Pensad que para entonces Intel comercializará Sandy Bridge, su próxima microarquitectura.

Especulación 5, prestaciones en enteros de Bulldozer:

Estimo unas débiles prestaciones single threaded en enteros para Bulldozer respecto a Intel Sandy Bridge y también respecto a Westmere. Sin duda, en el terreno multi thread su potencia representará un gran avance para AMD en enteros y en cálculo matemático en coma flotante (FPU) y probablemente luchará en igualdad con Intel en FP y quizás en enteros.

Según los ingenieros de AMD (espero que sea así y no hable el departamento de marketing) se espera una mejora de un 80% en enteros gracias al segundo core integrado. Como vemos subrayan el aspecto multi thread pero nadie habla sobre su velocidad en cálculo con un solo hilo de ejecución.

Como podéis inferir, me inclino por la segunda opción en la anterior Hipótesis 1.

Según la interpretación mayoritaria Bulldozer iba a disponer de cuatro pipelines de enteros (ALUs) por core (8 por cada módulo de dos INT cores). Ahora que conocemos la realidad, la lógica y el sentido común se han impuesto y AMD no ha producido un mega procesador de 600 mm2 para contentar a algunos fans exacerbados…

AMD Bulldozer 32nm:

En su lugar AMD ha hecho lo más lógico, ha asumido la brutal maestría de Intel en el terreno del procesamiento de enteros (gracias sobretodo a lo aprendido sobre branch prediction en la era NetBurst) y ha decidido acercarse lo máximo posible en rendimiento pero dentro de los límites económicos y de work force (capacidad de ingeniería, man hours) a su disposición.

AMD ha diseñado un eficiente procesador en el que se comparten algunos componentes para, por un lado reducir la superficie del chip y bajar costes y por otro lado poder integrar más cores (de menor superficie) en un chip monolítico.

Cada INT core solo aumenta la superficie del módulo en un 12 %.

Cada INT core solo aumenta la superficie del módulo en un 12 %.

En mi opinión, la FPU compartida en un módulo (con dos INT cores) y con capacidad SMT de ejecutar dos threads simultáneos es un movimiento súmamente elegante de ahorro de recursos y optimización de rendimiento.

Las etapas de fetch:

Fecth significa la carga de instrucciones desde la caché L1i (de instrucciones) en este caso de 64 KB y 2 vías (preservando el ya arcaico diseño Athlon).

Por fin AMD ha diseñado un fetch 4 issued, es decir carga 4 streams de instrucciones / ciclo dirigidos a los 4 decoders posteriores. Muy probablemente en bloques totales de 32 bytes / ciclo como Shanghai (Phenom II) y Barcelona.

El decoder de Bulldozer:

El encargado en las CPUs X86 de traducir las farragosas e irregulares instrucciones X86 a un formato manejable por un procesador moderno es el decoder. Este las transforma en cadenas de operaciones simples de estilo RISC.

La etapa de decodificación ha sido ampliada a 4 vías desde Phenom II y sus antecesores (3 vías), con ello iguala a Core 2 y Nehalem.

Los schedulers:

Hay tres schedulers discretos en un módulo Bulldozer:

- Scheduler del INT core 0

- Scheduler del INT core 0

- Scheduler de la FPU de 256 bit

Los schedulers de enteros son unificados a diferencia de los anteriores diseños de MD en que se utilizaban schedulers diferentes para las ALUs y las AGUs.

Cada INT scheduler tiene 4 puertos que sirven a las 2 ALUs y las 2 AGUs de cada INT core.

El FP scheduler también cuenta con 4 puertos que alimentan a la gran FPU de 256 bit, pudiendo contener instrucciones de dos threads diferentes, podemos decir que es una FPU con SMT de 2 vías.

Los INT cores de Bulldozer:

AMD ha reducido el ancho de las unidades de ejecución de enteros de Bulldozer respecto a los anteriores K10.5 (Phenom II 45 nm), K10 (Barcelona 65 nm), K8 90 nm – 130 nm y K7 Athlon 130 – 180 –250 nm.

Desde el venerable AMD K6 ninguna CPU de AMD ofrecía solamente dos pipelines de enteros ALU por thread. Esta es en mi opinión la mayor falla del diseño.

Bulldozer integra en cada INT core lo siguiente (el doble en cada módulo):

- Scheduler de enteros

- 2 ALUs

- 2 AGUs

- Caché L1d de 16 KB - 4 way (vías de asociatividad)

Para el lector poco avezado parece un desastre respecto a un Phenom II:

- Schedulers de enteros y AGUs separados

- 3 ALUs

- 3 AGUs

- Caché L1d de 64 KB - 2 way (vías de asociatividad)

Vemos un 50% menos de unidades de proceso en Bulldozer (de 3 a 2).

Realmente y en la práctica AMD arrastraba limitaciones importantes relacionadas con la extrema rigidez de proceso de los 3 pipelines de enteros y un scheduling realmente primitivo respecto al contemporáneo de Intel. En Bulldozer se han corregido brillantemente estos problemas.

El scheduler es común para las 2 ALUs y las 2 AGUs dando mayor flexibilidad para procesar las instrucciones en uno u otro pipe y permitiendo más libertad de posicionamiento a las instrucciones aumentando la ocupación de las unidades de ejecución y con ello el rendimiento.

Espero velocidades de proceso single threaded de enteros comparables entre Bulldozer y Phenom II clock for clock y core for core, lo que es todo un logro teniendo en cuenta la reducción drástica de hardware.

En proceso multithread la mejora será importante, habrá un 33% más de INT cores por chip (pasaremos de 6 a 8 cores) y gracias a otras mejoras es muy lógico pensar en un incremento de un 50% global en velocidad.

La FPU unificada de 256 bit:

La FPU contiene las siguiente unidades:

- Dos FMACs de 128 bit (SSE y AVX)

- Dos unidades de 128 bit de proceso Packed INT (SSE)

Es capaz de procesar desde antiguo código X87 de 80 bit pasando por SSE de 64 y 128 bit hasta AVX de 256 bit, en este caso en paralelo con las dos FMACs de 128 bit.

Además puede ejecutar instrucciones de dos threads distintos, dándole capacidad SMT.

Las cachés L1 de Bulldozer:

Todavía con datos preliminares, AMD las ha diseñado de este modo:

- L1d (datos) discreta por core. 16 KB y 4 vías

- L1i (instrucciones) compartida por los dos INT cores. 64 KB y 2 solo vías

El tamaño de L1d es bajo, muy bajo. Lo compensa algo su asociatividad de 4 vías (algunos hablan de 8 vías). En cualquier caso su hit rate será claramente menor que las L1 de Nehalem o Westmere, sobre 0.70 veces inferior.

Esto provocará una mayor “presión” sobre la L2 de gran tamaño (además, compartida por cada pareja de INT cores). Espero (más bien deseo) que la L1d sea de 8 vías...

La L2 de Bulldozer:

La L2 de Bulldozer es un verdadero equilibrio de diseño:

- Desde el punto de vista de los INT cores sería mejor un diseño con dos L2 discretas de bajísima latencia (como en Intel Nehalem).

- Visto desde la FPU compartida en el módulo es imperativo que solo haya una L2 y claro debe ser de mayor tamaño, sobre 1 o 2 MB. Aunque esto forzará latencias altas, lógicamente de más de 15 ciclos.

El diseño final parece que será una L2 compartida por 2 INT cores y la FPU de un tamaño de 1 o 2 MB y 16 vías de asociatividad. Así se ahorra área y transistores creando un diseño económicamente más eficiente.

Conclusiones:

Me remito a lo que escribí a principios de 2010:

Espero, por el bien de la sana competencia, que AMD sea capaz de llevar al mercado en 2011 esta nueva arquitectura. El proceso de 32 nm SOI high-k metal gate de Global Foundries parece bien planteado sobre el papel y ya hay algunas muestras funcionales que incitan al optimismo.

El único pero que yo veo al diseño es en algoritmos single thread que todavía (y por bastantes años) pueblan el ecosistema software de nuestros días. La mera instalación de un programa o una suite de ofimática, la navegación por internet y numerosas tareas del sistema operativo son todavía single threaded y así persistirán por largo tiempo dadas las grandes dificultades para su paralelización.

Sencillamente hay ciertos procesos que no son paralelizables y para ellos necesitamos anchos procesadores con múltiples y cortos pipelines y grandes motores de ejecución fuera de orden (OOO Execution, Out Of Order Execution) funcionando a altas frecuencias.

Para más información os remito a los artículos citados en el principio y a próximas ampliaciones.

Si consideras útil el contenido de este Blog, ayuda a mantenerlo ojeando algunas de las ofertas que consideres interesantes de nuestros anunciantes.

Un módulo Bulldozer consta de dos cores de enteros.

Un módulo Bulldozer consta de dos cores de enteros.