AMD ya comercializa los nuevos procesadores quadcore basados en el nuevo núcleo Shanghai de 45 nm. En este artículo hablaré sobre las diferencias con el AMD Barcelona de 65 nm y haré una estimación de sus prestaciones así como de sus frecuencias esperadas.

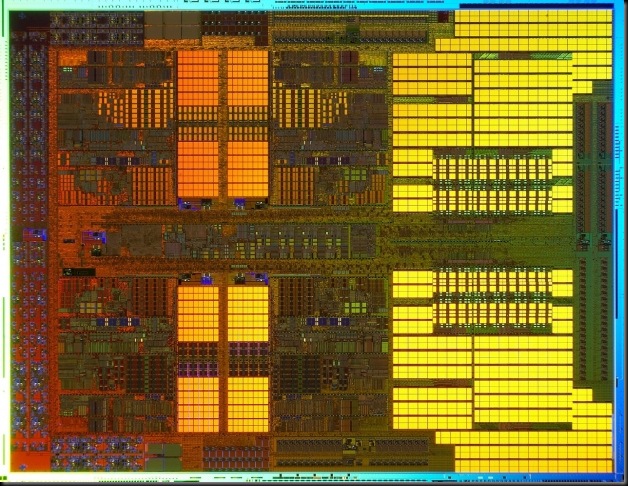

Fotografía del die de AMD Shanghai 45nm

Cambios microarquitecturales

Respecto al AMD Barcelona, utilizado en los Phenom y Opteron quadcore de 65 nm, Shanghai aporta algunas mejoras importantes y algunos otros trucos para incrementar el rendimiento.

Shanghai estará fabricado en el nodo de 45 nm (por las actuales fábricas de AMD en Alemania) con una superficie total estimada de 258 mm2 (frente a los 283 mm2 de Barcelona) contando con unos 758 M de transistores (frente a los 483 MT de Barcelona).

Esquema de Shanghai

Caché L3 de 6 MB

En primer lugar Shanghai aumenta el tamaño de la caché L3 de 2 a 6 MB siendo una cantidad más acorde al diseño del procesador y acercándole a las cachés de sus rivales de Intel (Core 2 y Core i7).

La arquitectura de caché queda del siguiente modo:

- L1 de 64 KB + 64 KB (Datos e instrucciones)

- L2 de 512 KB por núcleo

- L3 común para los cuatro núcleos de 6 MB (6144 KB)

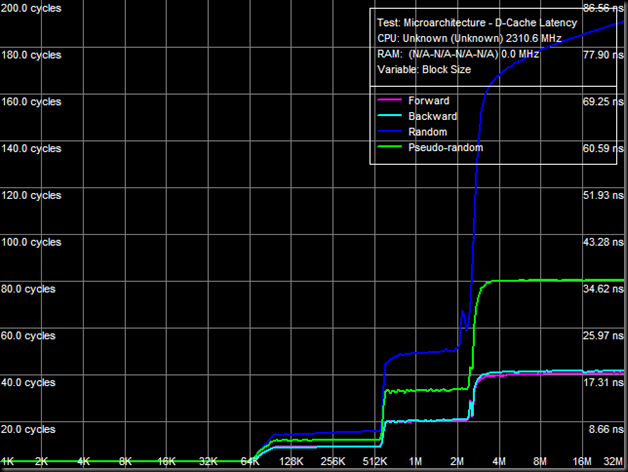

Un amplio espectro del software actual se beneficiará significativamente del nuevo tamaño de la caché L3, ya que 2 MB para cuatro procesadores se antojaba claramente insuficiente, recordemos el gráfico siguiente:

Latencias de L1, L2, L3 y RAM en un Phenom 9600 BE stepping B2 sin TLB Patch

Podemos ver que la zona de L3 es exigua y gran parte del código actual no se ajusta a esas dimensiones y más pensando en entornos reales multitarea, en los que se ejecutan concurrentemente diferentes programas con ubicaciones y datos diferentes en memoria y con sets de trabajo globales superiores a los 2 MB.

Latencia y frecuencia de L3

Además la L3 de Shanghai no solo mejora su capacidad sino también en velocidad. Su frecuencia aumenta (en los primeros modelos) a 2.2 GHz desde el máximo de 2 GHz de Barcelona.

Arquitectura de caché exclusiva de Shanghai. Fuente AMD Developer Blogs

Se ha rediseñado su esquema de acceso, reduciendo de manera drástica su latencia (latencia efectiva medida) de 53 ciclos en Barcelona a solo 43 en Shanghai (igualando de este modo a Core i7 en su latencia L3). Este es un punto muy importante y en innumerables ocasiones he criticado (a veces duramente) este aspecto de la arquitectura K10. Esta mejora en latencia L3, aportará por sí misma una buen plus en prestaciones.

Extraído de AMD Developer Blogs, Larger L3 in Shanghai. Part I:

" Latency reduction in the new L3 cache:

Within the processor the L3 cache is part of the north bridge subsystem and runs at the North Bridge (NB) frequency. Hence the L3 hit latency is also dependent on the NB frequency.

"Shanghai" has a best case latency of 29 CPU clocks, whereas "Barcelona" had a best case latency of 34 CPU clocks. So the lower latency to data stored in L3 cache should also help to significantly boost performance. "

Hardware Prefetch

Los arquitectos de AMD han trabajado también en el rediseño y mejora del mecanismo de Hardware Prefetch, que funciona precargando en caché los datos e instrucciones que el algoritmo estima serán necesitados posteriormente por el programa reduciendo así la latencia efectiva de la memoria y acelerando la ejecución.

Optimizaciones caché probing

AMD ha doblado el ancho de banda de test de L2 y L1 de cada núcleo para probar la coherencia de los datos (Probe Bandwidth). Recordar que AMD utiliza arquitecturas de caché exclusivas que fuerzan un alto tráfico de coherencia de cachés para comprobar que los datos en ellas son correctos y solo existe la "última versión" en todos los niveles de caché y en memoria principal.

Optimizaciones energéticas y de consumo

Shanhai se fabrica en 45 nm y cuenta con un ACP de 75 W en sus versiones Opteron de 2.3 a 2.7 GHz. Las versiones Phenom II de sobremesa probablemente llegarán a los 105W ACP a 3 GHz. La reducción de consumo y disipación térmica es muy importante destacando que un Opteron Shanghai a 2.7 GHz disipa bastante menos que un Barcelona a 2.3 GHz.

AMD ha dotado a Shanghai con un sistema que permite "dormir" a un núcleo "sin trabajo" totalmente moviendo sus contenidos de L1 y L2 a la L3 compartida permitiendo así parar el reloj de los cores no utilizados. En cualquier caso, este núcleo con el reloj detenido sigue consumiendo debido al Leakage. AMD ha llamado a esta tecnología Smart Fetch.

Para una excelente y divertida discusión sobre Leakage recomiendo la siguiente lectura de ArsTechnica:

The future of Prescott: when Moore gives you lemons...

Conclusiones:

En resumen, esperemos a verlos en acción en el terreno sobremesa. AMD parece que ha encontrado con Shanghai la senda del éxito y puede lanzar productos competitivos en la gama baja y media quadcore. Parece ser que inicialmente los nuevos Phenom II llegarán a los 3 GHz con el modelo 940 BE.

Probablemente un AMD Shanghai sea equivalente o ligeramente inferior en prestaciones a un Core2Quad a la misma frecuencia, lo que para AMD es un gran paso adelante.

Si el proceso de 45 nm evoluciona favorablemente para AMD y puede producir versiones superiores a los 3 GHz a lo largo de 2009 Shanghai será todo un éxito, pero no nos llevemos a engaño, Core i7 está a otro nivel, en prestaciones y ... en precio.

![amd_01[1]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEg8WN9irsBSKStWBOAzWGB-syHTIsCKVdJWjBT2MuDrHHgFJL3fPz9u1Y8V7VrKhYwjQ-wPBUUQIx_aFhNZodK7B-OqkhdZbzI4rKZ5BEMOIl-a54_duWED6avXqV9Bo7hT05qD_K3AUcI/?imgmax=800)

![Block_Diagram_for_Socket_F1207White_Background_375W[1]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhDuydzcTp6JnrAJW4he4Y2VS6NGNXxx7zcO932VWH9wAdkNpNUXVHhIKASWbtfhRpoIcuH6_2pGpPy-e2Owoikbmfi9oHi-xHriwC2goyzv-8hPAyZwXA4UfDLwHwkapmee9DBiEgodYI/?imgmax=800)

![L3_Cache_Architecture[1]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhaKs1SaOOXqoS36zGJBTjWljq88R1ix9G6rGoB4jVrImsJSXrKXl4zeQd_BpGpNWuSRD8wq2HKtK2s5VjPE2fz3r0SLFCSg-ogmWsTe9okDKT_eZlkQJKoWOR59SvcwS5fSTcU60UAsXU/?imgmax=800)

No hay comentarios:

Publicar un comentario

Nota: solo los miembros de este blog pueden publicar comentarios.