En el artículo anterior de LowLevelHardware y en otro de este mismo blog traté sobre el tema del fácil overclock del nuevo procesador Phenom II de AMD basado en el proceso de 45nm SOI DSL. Una peculiaridad notable de este proceso es su amplio margen para incrementar el voltaje unido a su menor disipación térmica.

Con los nuevos Phenom II podemos llegar a los 1,50 V (e incluso 1.55 V) sin problemas con un buen conjunto refrigerador-ventilador por aire. En este caso no ha sido necesario ir más allá de los 1.425 V pues el objetivo eran los 3.6 GHz.

Además para llegar a los 3.8 GHz es necesario aumentar la alimentación hasta los 1.525 – 1,550 V. A mi modo de ver excesivo para solamente 200 MHz más, no merece la pena …

Para estas pruebas he escogido un Artic Cooling Freezer64, un modelo ya clásico pero con un rendimiento excepcional dada la gran calidad de las soldaduras en su base y el uso de la pasta Artic Cooling MX2 ya pre aplicada.

Le excelente pasta MX2 de Artic Cooling.

Para un análisis micro-arquitectural en profundidad de este sistema en overclock recomiendo el artículo que publicaré próximamente en LowLevelHardware.

La base del Artic Cooling Freezer64.

Configuración del sistema:

- Procesador AMD Phenom II X4 940 Black Edition

- Placa Base ASUS M4A79-DeLuxe AMD 790FX – AMD 750

- 4 GB en dos módulos Kingston HyperX DDR2 1066 5-5-5-15 2T 2.2V

El procesador AMD Phenom (igualmente el Phenom II y el Core i7) es un diseño asíncrono. Diferentes partes del chip funcionan a distintas frecuencias relacionadas según unos multiplicadores fraccionarios.

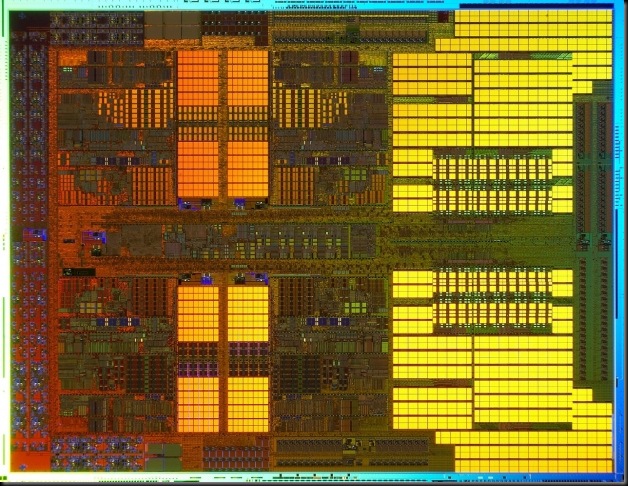

El procesador usado en las pruebas, un stepping RB-C2.

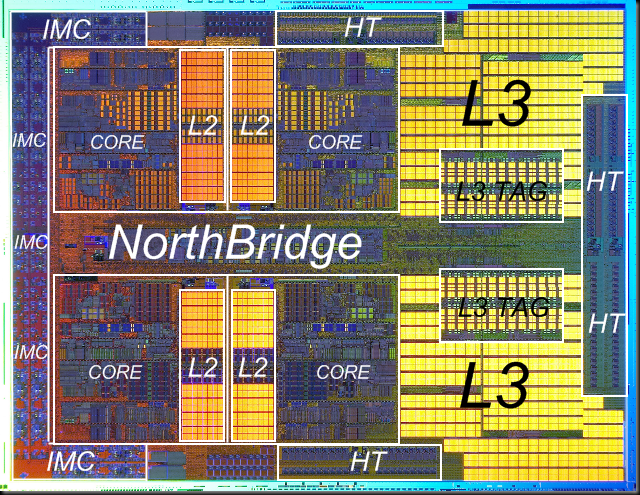

Un procesador de última generación como el AMD Phenom II o el Intel Core i7 se divide principalmente en dos secciones funcionales distintas y asíncronas:

- Los núcleos de ejecución

- El Uncore o “todo lo que no son los núcleos” que incluye a su vez:

- La caché L3

- Las controladoras de memoria (DDR2 o DDR3)

- Los buses de comunicaciones (HT o QPI)

-

AMD Phenom II, mapa funcional del die.

En el caso que nos ocupa, el Phenom II X4 940 BE, las frecuencias nominales son las siguientes:

- Los cuatro núcleos de ejecución funcionan a 3.0 GHz

- El Uncore a 1.8 GHz (incluyendo la caché L3 de 6 MB y las dos controladoras de memoria DDR2)

-

Los buses de comunicaciones HyperTransport a 3.6 GHz

Para aumentar las prestaciones, he modificado las frecuencias del siguiente modo:

- Los núcleos de ejecución funcionan a 3.6 GHz @ 1.425V (+20 %)

- El Uncore a 2.4 GHz (+33%) (incluye la L3 de 6 MB y las dos controladoras de memoria DDR2)

-

Los buses de comunicaciones HyperTransport a 3.6 GHz (sin cambios)

Dual channel DDR2 1066 unganged 5-5-5-18 2T 2.2 V.

Con este conservador overclock obtenemos prestaciones sobresalientes, nos interesa más una total estabilidad para una utilización continua y un consumo y disipación térmica controlados:

Phenom II X4 940 BE 3.6 GHz: unos excelentes 11 GB/s en Memtest86+ 2.11

2703 KB/s en WinRAR multithreaded.

En Fritz Chess benchmark ha obtenido 8853 Knodos (18.44X) y en wPrime 10.672s para 32 M. Debajo podemos observar como ha mejorado el rendimiento del sistema gracias al overclock:

| Phenom II X4 940 3.0 / 1.8 / Dual 1066 MHz | Phenom II X4 940 3.6 / 2.4 / Dual 1066 MHz | Diferencia % | |

| Fritz Chess | 7356 KN | 8853 KN | + 20.35 % |

| wPrime 32M | 13.202 s | 10.672 s | - 23.71 % |

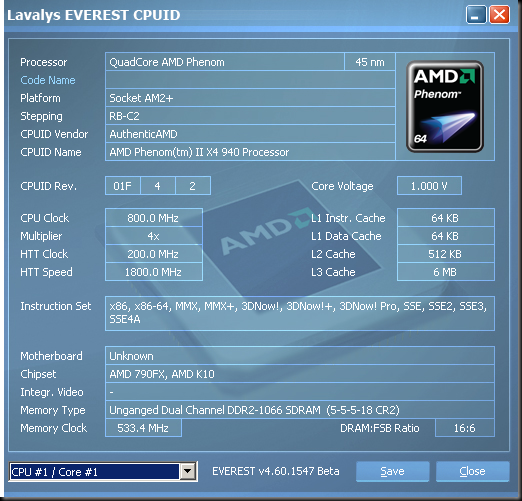

A 800 MHz Cool’n’Quiet con solo 1.000 V

De este modo no hemos perdido los beneficios de bajo consumo y temperaturas sobre los 25 – 28 ºC en los cores debido a que mantenemos activo el Cool’n’Quiet y los estados de ahorro de energía C states. Más información en las capturas de configuración de BIOS próximamente en LowLevelHardware.

En Everest el sistema ha obtenido unos excelentes resultados, con una latencia de memoria de 49.8 ns (179.3 ciclos a 3.6 GHz) y un ancho de banda de 8639 MB/s lastrado por el bus de 64 bit entre las IMC (controladoras de memoria), la L3 y las L2 de cada uno de los núcleos.

Quiero recalcar que el bus al que me refiero es individual para cada core:

Uno de los cores de un AMD Phenom tiene a su disposición 64 bits/ciclo a frecuencia del uncore (1.8 GHz nominales o 14.4 GB/s), lo que es insuficiente para un dual channel DDR2 1066 (17 GB/s).

Esta es una limitación de la microarquitectura y no podemos hacer nada para solucionarlo, excepto incrementar el reloj IMC/L3 (por esta razón he incrementado porcentualmente más esta frecuencia que la de los núcleos).

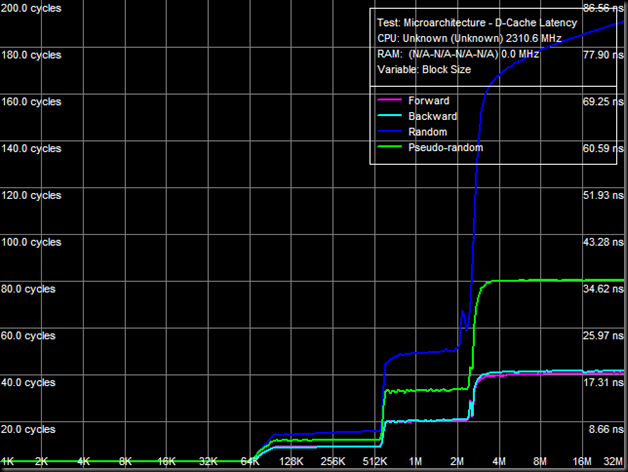

Phenom II X4 @ 3.6 cores / 2.4 GHz uncore en RMMA 3.80. Acceso single core.

Como vemos, en acceso single core, el ancho de banda en la zona de la caché L3 (de 640 KB a 6.5 MB en el gráfico) corresponde a unos 11.5 a 12 GB/s o unos 3.2 a 3.4 bytes/ciclo. Una transferencia insuficiente para hacer frente a un dual channel DDR2 1066 con una transferencia pico de 17 GB/s.

Recordemos que son datos en condiciones reales (transferencia real sostenida, no un pico esporádico máximo) y en acceso de un solo núcleo con los otros tres en estado idle (reposo).

En modo de acceso multithreaded estas velocidades mejoran mucho, como podéis ver al final del artículo en LowLevelHardware dedicado a este sistema en RMMT , llegando a un 86% del límite teórico.

Dado los voltajes conservadores y la cuidada preparación previa el sistema ha pasado sin problemas todos los tests de estabilidad con unas temperaturas en carga máxima de 61ºC a las 6h de Prime95 Blend.

Para un análisis pormenorizado de este sistema visita próximamente LowLevelHardware.

![amd_01[1]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEg8WN9irsBSKStWBOAzWGB-syHTIsCKVdJWjBT2MuDrHHgFJL3fPz9u1Y8V7VrKhYwjQ-wPBUUQIx_aFhNZodK7B-OqkhdZbzI4rKZ5BEMOIl-a54_duWED6avXqV9Bo7hT05qD_K3AUcI/?imgmax=800)

![Block_Diagram_for_Socket_F1207White_Background_375W[1]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhDuydzcTp6JnrAJW4he4Y2VS6NGNXxx7zcO932VWH9wAdkNpNUXVHhIKASWbtfhRpoIcuH6_2pGpPy-e2Owoikbmfi9oHi-xHriwC2goyzv-8hPAyZwXA4UfDLwHwkapmee9DBiEgodYI/?imgmax=800)

![L3_Cache_Architecture[1]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhaKs1SaOOXqoS36zGJBTjWljq88R1ix9G6rGoB4jVrImsJSXrKXl4zeQd_BpGpNWuSRD8wq2HKtK2s5VjPE2fz3r0SLFCSg-ogmWsTe9okDKT_eZlkQJKoWOR59SvcwS5fSTcU60UAsXU/?imgmax=800)