Siendo sincero debo admitir que me ha sorprendido gratamente el nivel de prestaciones de la nueva serie de CPUs FX de AMD basadas en el nuevo stepping dotado de cores Piledriver.

En un artículo de LowLevelHardware exploré detalladamente las mejoras que aportaba este core refinado, este nuevo stepping a la conocida micro arquitectura Bulldozer de AMD.

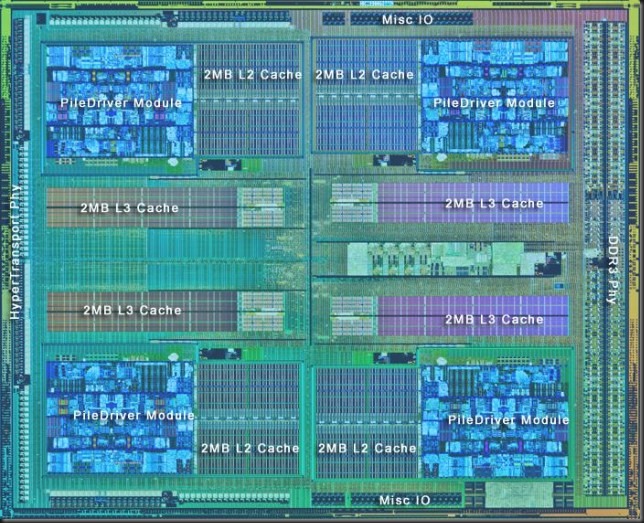

Piledriver module con sus 2 MB de caché L2.

Piledriver module con sus 2 MB de caché L2.

Podríamos sintetizar las mejoras en dos fundamentales:

- Por un lado una menor disipación térmica por core y un menor voltaje mínimo estable a una frecuencia dada. A igual frecuencia menor consumo y temperatura.

- Por otro lado un aumento IPC de un 5 a 30% en función de la carga de trabajo (enteros, branches, coma flotante, SSE, AVX,…) A igual frecuencia más rendimiento.

Gracias a estas dos mejoras AMD ha conseguido incrementar la frecuencia base del FX 8350 en 400 MHz.

AMD FX8150 vs. FX8350. Bulldozer vs. Piledriver.

AMD FX8150 vs. FX8350. Bulldozer vs. Piledriver.

En modo Turbo Core Vishera aplica el Turbo máximo en todas las situaciones, es decir, en carga máxima de un thread (ST, single threaded) o de varios threads e incluso 8 threads simultáneos (MT, multi threaded):

Turbo Core en FX8150 Bulldozer.

Turbo Core en FX8150 Bulldozer.

Podemos decir, para simplificar, que en Vishera el estadio intermedio Turbo Core desaparece.

En la práctica, medido por mí mismo, un Vishera FX8350 a 4 GHz en Prime95 Blend 4 GB consume exactamente lo mismo a un Bulldozer FX8150 a 3.6 GHz a voltajes nominales.

Bulldozer module 32 nm SOI HKMG.

Bulldozer module 32 nm SOI HKMG.

Como deduciréis fácilmente, Vishera aportará un 11% más de frecuencia en cargas paralelas y en cambio no incrementa nada en cargas single threaded. Por ello en cargas ST el rendimiento solo aumentará por el incremento de IPC y en cambio en cargas MT se sumará el 11% de frecuencia nominal al incremento IPC.

Undervolting

A esto debo añadir que tanto en los antiguos FX Bulldozer como en los nuevos Vishera AMD ha sido bastante exagerado en cuanto a los voltajes a los que vende sus CPUs. Normalmente son absolutamente estables a voltajes 0.100 – 1.150 V inferiores a los nominales. Con ello además ganamos unos 20 – 30 W en consumo y 10 – 15 ºC de temperatura. Merece la pena hacerlo aunque con ello perdamos horas o incluso a veces algunos días.

AMD debería hacer este proceso en fábrica pero resulta laborioso y por ello caro. De este modo saca al mercado las CPUs a un voltaje excesivamente prudente para asegurar su estabilidad sin probar individualmente en exceso cada uno de los chips para ajustar individualmente su voltaje.

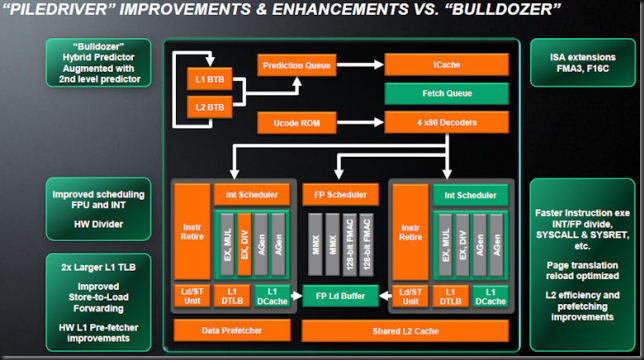

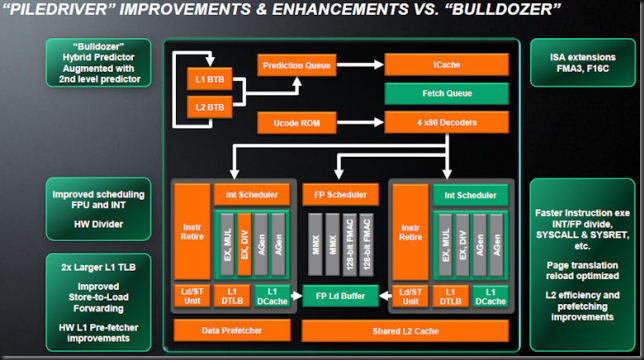

Piledriver. Mejoras micro arquitecturales respecto a Bulldozer.

AMD ha mejorado Bulldozer en muchos aspectos aunque sin cambiar nada importante del diseño, de hecho Piledriver no es más que un stepping más avanzado del mismo core.

Se ha mejorado el Branch Prediction, algo crítico en este diseño debido a su larguísimo pipeline. Esto mejorará el rendimiento sobretodo en cargas de enteros.

Se ha activado la unidad de división de enteros (INT Div, iDiv) que estaba deshabilitada en Bulldozer por un fallo de diseño, como comenté en Abril de 2011 en mi artículo:

“ EX0 contiene una unidad de división de enteros parcialmente pipelinizada y con latencia y capacidad de proceso variable en función de la precisión. Aunque examinando detenidamente la documentación parece que más bien se trata de una unidad “virtual” ya que la instrucción IDIV se decodifica en el Microcode Engine y se secuencia en instrucciones sencillas ALU que se ejecutan en EX0. Además incluye una unidad para LZCNT y POPCNT. “

Efectivamente, en Bulldozer, la unidad iDiv no estaba habilitada y por ello la latencia y velocidad de las divisiones de enteros eran tan decepcionantes. Por fin, en Piledriver se encuentra habilitada.

Se ha doblado el tamaño del L1 dTLB (TLB de datos de nivel 1). Para el que quiera amplia información sobre para que sirve un TLB le remito a algunos artículos pasados.

En total todas estas mejoras aumentan el IPC de un 5 a 30%, en general sobre un 10%. En el caso del 30% es más por un rendimiento terrible de Bulldozer en algunas tareas que por méritos de Piledriver.

En cualquier caso podríamos caracterizar las prestaciones de Piledriver en el AMD FX8350 del siguiente modo:

- Cargas de trabajo de enteros con excelente paralelización y con carga máxima en los 8 INT cores. Ejemplo: compresión de datos en WinRAR o 7zip LZMA2. Prestaciones generalmente muy superiores al Core i5 3570K y superiores al Intel Core i7 3770K.

- Cargas de trabajo de coma flotante con excelente paralelización y con carga máxima en las 4 FPUs FMACs con 8 threads.

Ejemplo 1: Rendering, cálculo matemático. Prestaciones generalmente bastante superiores al Core i5 3570K y ligeramente inferiores al Core i7 3770K. En PovRay en cambio el más rápido y por buen margen es el FX8350.

Ejemplo 2: Edición y codificación de video x264 / H264. Prestaciones generalmente superiores al Core i7 3770K y muy superiores al Core i5 3570K.

- Cargas de trabajo principalmente de enteros con baja paralelización y raras veces con carga máxima en 4 INT. Ejemplo: SysMark 2012, compilación y usos multitarea de la máquina en Windows con varias aplicaciones a la vez. Prestaciones muy similares o algo inferiores al Core i5 3570K (como mucho un 10%).

- Cargas de trabajo de enteros single thread o con paralelización muy leve. Ejemplo: instalaciones de software, instalación de sistema operativo, javascript. Prestaciones inferiores a Core i5 3570K hasta un 40% en proceso javascript.

Si hacemos la media el FX8350 nos da un rendimiento superior en un 5% al Core i5 más alto de gama, el i5 3570K que está situado por encima en precio (unos 20 – 30@ más).

El Core i7 3770K se sitúa en un nivel de prestaciones superior gracias al Hyper Threading como atestiguan sus más de 150€ extras de coste.

Conclusiones

Lo más positivo que puedo sacar de Vishera es su notable aumento de velocidad de trabajo en aplicaciones ofimáticas respecto a Bulldozer (ha mejorado más de un 20%) y el hecho de haberse convertido en el rey en prestaciones en temas de video, sobretodo en coding x264. En estos casos supera incluso al excelente y mucho más caro Core i7 3770K.

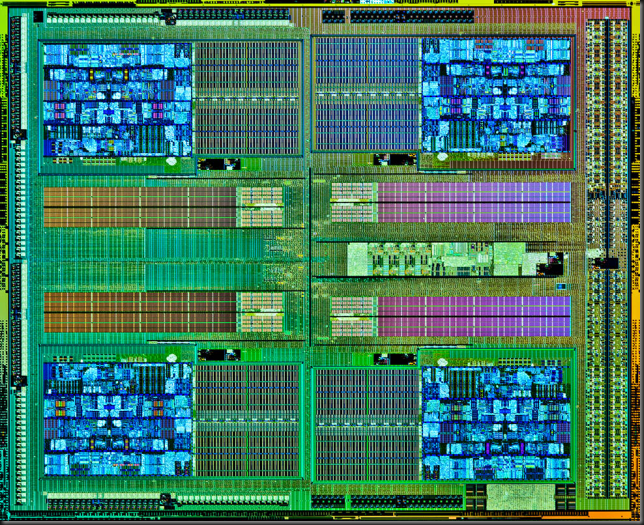

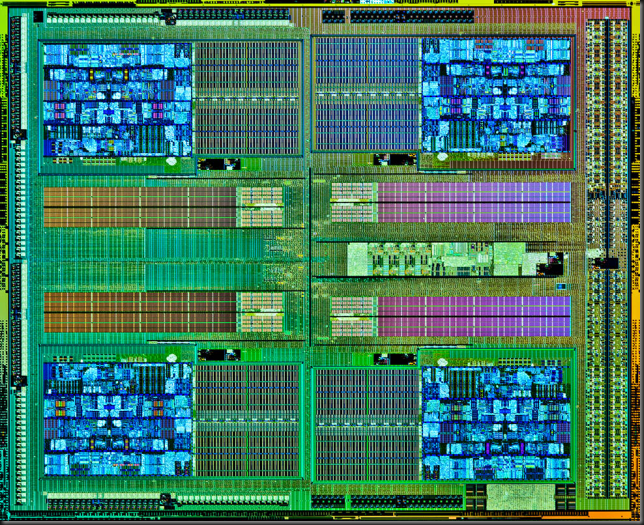

El die completo del procesador AMD FX 8350 32 nm.

El die completo del procesador AMD FX 8350 32 nm.

Vishera mantiene exactamente los niveles de consumo y disipación térmica de los anteriores AMD FX con un rendimiento medio en cargas multithread de un 20% (ayudado por los 400 MHz extras) superior y un 5 – 10% en cargas single thread (con igual frecuencia).

Post Scriptum

Animo a los posibles compradores de estas CPUs a cambiar el funcionamiento nominal de Turbo Core. AMD ha dejado invariado el Turbo Core con carga single threaded o dual threaded a 4.2 GHz respecto a Bulldozer.

En Bulldozer FX8150 la disipación térmica y consumo era prácticamente igual con cargas MT de 8 threads (3.6 GHz) que en single o dual threaded (4.2 GHz) e igual a 125W.

En Vishera, en cambio, con cargas de 8 threads (4.0 GHz) llega a los declarados 125W en Prime95 pero con cargas single o dual threaded (4.2 GHz) se queda corto marcando unos 100 – 105W.

Los samples que he probado del AMD FX8350 son absolutamente estables en cargas single o dual threaded a voltaje nominal a 4.6 GHz y manteniendo siempre la disipación térmica por debajo de los 125W nominales. Para ello, en BIOS, cambio manualmente el funcionamiento de Turbo Core aumentando el multiplicador máximo a 46X.

En este caso conseguimos otro 9 – 10 % adicional de velocidad en casos ST (single threaded), el talón de Aquiles de esta micro arquitectura.

Echad un vistazo a la web de mi nueva empresa, un proyecto de gran envergadura que llevo preparando hace más de un año.

Os lo recomiendo para diseño de sistemas de altas prestaciones optimizados al límite:

Allí tenéis a vuestra disposición el formulario de contacto, para consultas sobre este artículo hacedlo más abajo en la sección de comentarios.

Y mi nuevo Blog de contenido muy técnico y actualizado donde encontraréis artículos míos sobre hardware, procesadores y sistemas y también otros posts de expertos programadores e informáticos sobre otros temas de actualidad:

Si consideras útil el contenido de este Blog, ayuda a mantenerlo ojeando algunas de las ofertas que consideres interesantes de nuestros anunciantes. Gracias de antemano.

El que tenga dudas o aportaciones tiene para ello la sección de comentarios, intentaré responder a todos y con la máxima claridad. Los Blogs deben de ser lugares de intercambio y agradezco vuestro feedback.

Carlos Yus Valero – informaticapremium ![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEg6D8ZeIzNza_ml04UvHJZf7oUATyWeLN79Z3HFr3PaG5fvWff_Jzh08S7vz7AMvqivt899oRGZ-UXea8r3I3mkOanrGVfyjv5rBAN4VhthOUOvkpWBQny1mrtQbTgD2KrgQkGDxCckpkU/?imgmax=800)

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjYM7AUkMrTts40mxv86Rbc-tQf6s_2LfEMBwQxfF8UIly1w_u_C1kROsMbLiUcxQjJY8C5QTzzAOb6f9cUwZ31R8B1oRnjEDaiSCMEUHIhZTnF4tokix33UZth5A9r4zbxGNDqM3GZriw/?imgmax=800)

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEiMPDAE1_TzqSb70iWLAlW0fhrrRU7FKx-gGzzP_5EVy4USnGOUMgIfjXMhdBT4HD3PoZCkxgiRLqT5FCHq7TNL6DGPoQEtRkNXstANl6JD86uEgGIuc1iiuIyFtR384_PHBEJnrcowGg8/?imgmax=800)

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEj4iriqZf_w9Ldn-JSEtfZV2TSOvFSH7D1MoSxZnPSx7tR-2HLDNbq_p3rTvvaTW79-fIGyfePYmkfJg8Sqvr5oAO5bcr_bX_ehI5QVOkmybmdn5Xj7TOpDK7K1xww_i4OjN2QbsOZd7to/?imgmax=800)

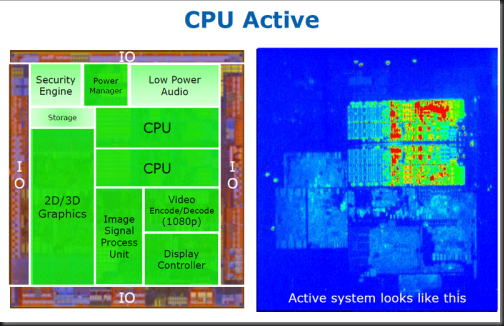

AMD Kaveri 28nm.

AMD Kaveri 28nm.![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEingNELLT-9UC5QCHJd12vLfy4j1016HQCn-e7ugFQpcQls9AlK3EMKXpp2zlHP4619nBg4FdS1miwyTR8HsboWR3PmNbV-cgXEe0_sOJJvb9_PSV-naMIvjlIc6w1K0uzdCELmyjdCwOQ/?imgmax=800)

![semim[6] semim[6]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjiGrN2Z_YLbW-9RGJWbbQMKwxxvlv3y6bSh9uUfvYGynuXDilUbhb4WQq7F_z6dVt-NKjs-wYcVWaVVRpZ92FKUtMkJ_nioDTKWfBhgh98IB1KC8gMXoL7tordbTX9fSCEC0apFpuafek/?imgmax=800)

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjA-rD6qEGqZgqZGDufwzXWStJl1zQG6x8pUTTv_ornPlxwBdbEiKteiWlDtYFzotF_hXFNt7VmOmqT4ZebhfdRwe08uSfqCBKIREnI9S6gHa0dg-5HXyKVqEVQ_5ouf4cCOblZjuYBoSQ/?imgmax=800)

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhOI77A21Skb_fM2kdzipgvzFsrxVgY0D8un95FwrFwV9xzeXkmXvNcObbre7nFXem3bYy1DKcSF3zXEmkrkTnaAfAN-ezIUK0VbHz5tY3Rq7rnyOkychmxQREcFnS2eTinmc2u1cWFAsM/?imgmax=800)

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEg6D8ZeIzNza_ml04UvHJZf7oUATyWeLN79Z3HFr3PaG5fvWff_Jzh08S7vz7AMvqivt899oRGZ-UXea8r3I3mkOanrGVfyjv5rBAN4VhthOUOvkpWBQny1mrtQbTgD2KrgQkGDxCckpkU/?imgmax=800)

![informaticapremium-logo-150px[3] informaticapremium-logo-150px[3]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEgTigP8glSCuKfMqkSIYIM1XG2Q91dcxHs6A5Jjlam1V7K8OiZ0mBUzrXj24HjAEgA2QEl-X_fOjLISRwQtKeP2CfBXCh0gzwT0I9L5mdxC6BTcDGRWT5ed2GYpjZ62U9uqK47YkqzRhfk/?imgmax=800)